上一章我们介绍了基于SR锁存器改造得到的D触发器,D触发器可以用于数据的存储,这对我们后续制作寄存器能够起到至关重要的作用。但是在着手制造寄存器之前,我们还需要先了解一下于寄存器息息相关的、用于控制CPU中数据流动的总线和三态门。

总线

在从零开始的手搓CPU(0)——前言与CPU基本结构中我们提到过,CPU中的总线用于负责连接各个模块,用于数据传输,还负责与外部设备、内存、芯片组(所谓的南桥之类的)进行数据通信,如果计算机中有多个CPU(核心),也负责CPU间通信。

正如之前所说,CPU中的总线实际上就是一堆连接到各个模块之间的线。在这一章,我们将了解到总线是如何连接到CPU中的各个模块的。

既然是用来连接各个模块的,那么先来回顾一下CPU中有哪些模块。首先是寄存器,寄存器是用来保存数据的,所以我们寄存器至少应该具有输入和输出的功能,所以我们会给寄存器设计两组引脚,分别是输入引脚和输出引脚,它们都连接到总线中。

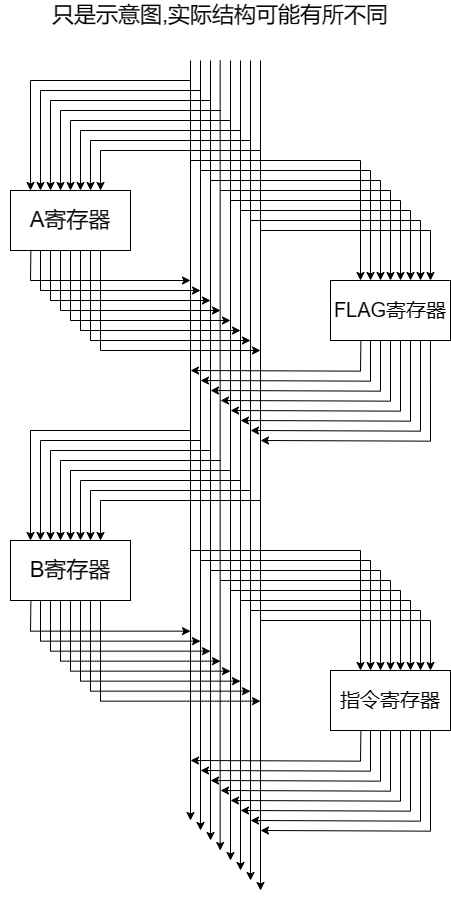

示意图(开dark模式可能看不清)

示意图(开dark模式可能看不清)

如上图所示,中间与所有寄存器相连的八条线就是总线,总线与每一个寄存器直接相连,所以我们可以在不同的寄存器之间相互传递数据。实际上,总线的数据是不讲究方向的(因为都是电线,电荷虽然有移动方向,但是通电以后,所有接到总线的模块都会有电流经过),所以我们可以将数据输入寄存器的引脚和寄存器输出数据的引脚合并到一起,也就是说,寄存器有一组引脚和总线相连即可,这组引脚可以分别进行输入和输出的工作。

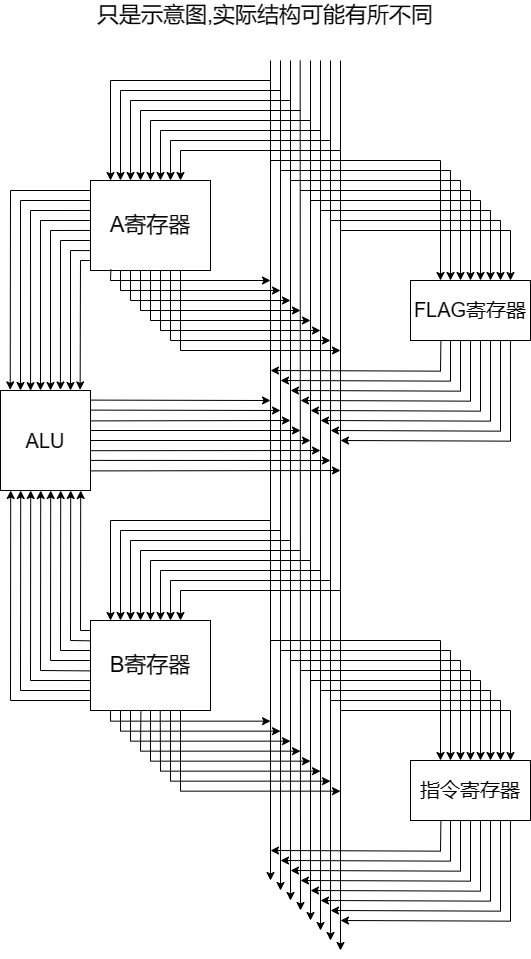

其次是ALU,我们之前提到过,ALU在进行计算时,会分别从A寄存器和B寄存器(通用数据寄存器)中读取立即数,然后经过计算,输出到总线或结果寄存器,所以ALU到总线的连接如下:

带ALU的总线示意图

带ALU的总线示意图

再然后是控制器,控制器一般不直接和总线相连,这里就不详细介绍了,等后面做到控制器部分再说。

三态门

正如我上方所说,不管是输入输出两组引脚分别连接到总线,还是只有一组引脚连接到总线,寄存器都是和总线直接相连的。但实际上,我们并不希望在任何时候,寄存器都把值放到总线上,也不希望在任何时候,总线都把值存到寄存器内。所以我们需要一个开关,用于控制数据的流动,开关关掉时,不让数据从总线存到寄存器,或不让寄存器把数据放到总线上。

这个开关,叫三态门。

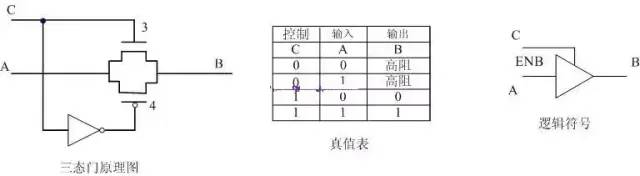

正如其名所述,三态门有三个状态,分别是逻辑输出0、逻辑输出1、高阻态。其中,高阻态就是用来将逻辑门同系统的其他部分加以隔离的,在我们不希望总线的数据对寄存器操作,或不希望寄存器对总线进行操作时,就会将三态门置于高阻态。

三态门(大概的)原理图

三态门(大概的)原理图

如上原理图,在上面的三极管激活时,输出端(LED端)接到5v电压,输出高电平;如果上面的三极管关闭,下面的三极管激活,则输出端接地,输出低电平;如果两个三极管都关闭,则输出与输入隔断开;如果两个三极管皆激活,则5v直接接地,电流不过输出端(理论上也会有极小电流,可以忽略)。